People also ask, how do you program a CPLD?

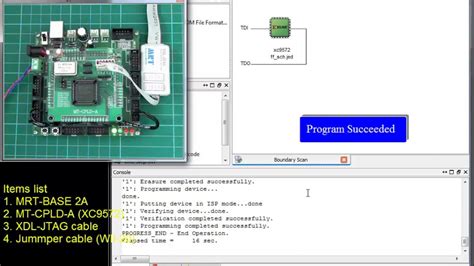

Open the iMPACT programming tool from the ISE Design Suite project panel under Configure target device->iMPACT. Choose the option to create a boundary scan file, and set the type to XSVF. Give the XSVF output a file name and then add a compiled CPLD image (ex1. jed) when prompted to add a device.

Beside above, what is a macrocell in CPLD? Macrocells are the main building blocks of a CPLD, which contain complex logic operations and logic for implementing disjunctive normal form expressions. Macrocells can also be defined as functional blocks responsible for performing sequential or combinatorial logic.

Beside above, how do I program Xilinx?

Programming the FPGA

- Select Xilinx Tools > Program FPGA.

- In the Bitstream and BMM File fields, specify the bitstream (. bit) and Block RAM Memory Map (.

- SDK automatically detects the processors in the system and shows them in a table at the bottom of the window. Under Software Configuration, select the executable (.

- Click Program.

What is a .JED file?

A JED file is a Xilinx JEDEC hardware configuration file. It is used for programming complex programmable logic devices (CPLDs), such as computer processors. ISC files, which are used for programming FPGA hardware devices. Important: JEDEC is an acronym for "Joint Electron Device Engineering Council."